Здесь мы собираем самые интересные статьи, интервью, репортажи и многое другое.

Новое поколение решений для корпусирования интегральных схем. Часть 4

Фелтон К., Вертянов Д., Евстафьев С., Сидоренко В., Горшкова Н.

Проектирование и верификация гетерогенных корпусов микросхем, микросборок вводят новые требования и ограничения к функциональным возможностям, уровню интеграции и масштабируемости САПР. Разработка сложных корпусов требует взаимного сотрудничества между дизайн-центрами, компаниями OSAT, фабриками и производителями EDA решений. В заключительной части статьи рассмотрены основные этапы и программные модули лучших в своем классе решений верификации и тестирования сложных гетерогенных корпусов микросхем для эффективной и безошибочной передачи проекта на производство.

Многокристальная разнородная (гетерогенная) и однородная (гомогенная) сборка кристаллов продолжает оставаться перспективным направлением в части получения законченных устройств, состоящих из нескольких кристаллов. Данное направление основано на подходе More than Moore, которое остается проверенным способом интеграции нескольких кристаллов, изготовленных по различным технологическим процессам, а также предполагает уменьшение геометрических размеров и увеличение функциональности электронных устройств. Технологии гетерогенной интеграции предназначены для расширения функциональности электронных устройств, более быстрому выходу на рынок и устойчивости их к проблемам, связанным с выходом годных кристаллов.

В первой части статьи рассмотрены и проанализированы основные проблемы современных технологий корпусирования ИС, маршрут проектирования, верификации, подготовки к производству гетерогенных многокристальных и многоподложечных сборок по технологии цифрового двой ника. Вторая часть статьи посвящена многоуровневой и межплатформенной интеграции (реализовать которую позволяет технология цифрового двой ника) с анализом целостности сигналов на уровне корпуса микросхемы, микросборки, а также экстракции параметров поведенческой модели. В третьей части статьи рассмотрены масштабируемость и широкий функционал, необходимые для работы с современными и перспективными корпусами ИС, сформулированы требования для предсказуемой безошибочной передачи данных о проекте на производство. Заключительная часть статьи посвящается основным этапам и программным модулям лучших в своем классе решений верификации и тестирования сложных гетерогенных корпусов микросхем для эффективной и быстрой передачи проекта на производство.

Golden Signoff

Golden Signoff ‒ термин, означающий полное соответствие проекта требованиям фабрики в части выполнения проектных норм (DRC – Design Rule Check), рекомендаций по повышению выхода годных (DFM – Design for Manufacture) и полную готовность к передаче на производство. Разработчики используют специализированные программные средства для проверки правил проектирования на соответствие технологическим нормам и требованиям, заложенным в PDK / PADK, которые предоставляет полупроводниковая фабрика или компания по сборке и тестированию изделий микроэлектроники (OSAT). В случае работы со сборочным производством требуется дополнительно согласование конструкции изготавливаемых подложек (интерпозера, корпуса).

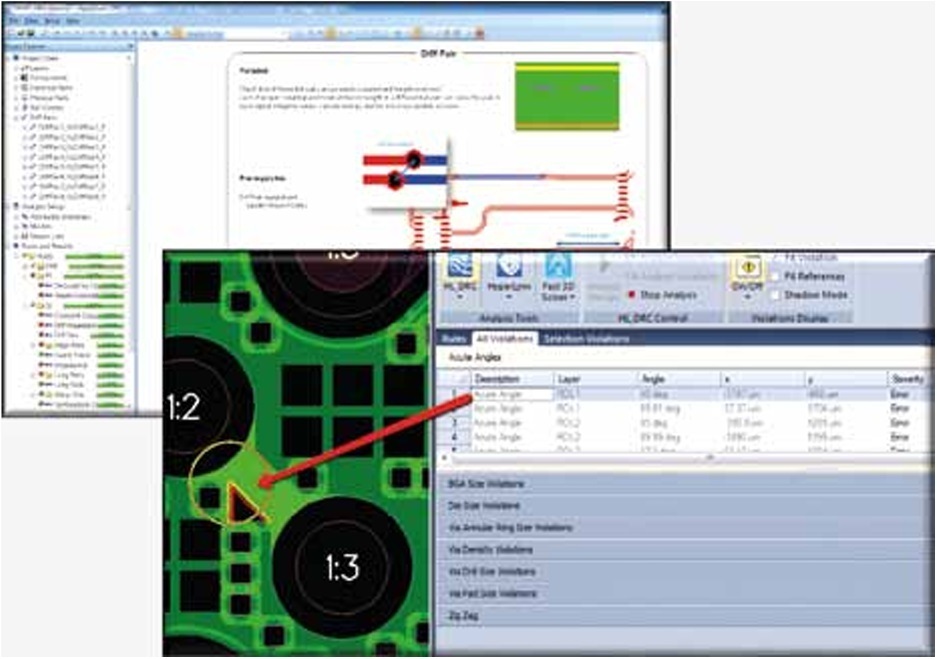

При передаче проекта современного корпуса ИС на производство, то есть при осуществлении golden signoff, требуется широкий набор проверок, иначе выход годных изготовленных изделий не достигнет планируемого объема и прогнозируемые затраты на сборку и испытания превысят ожидания. Примером этого может служить соблюдение правил DFM, которые являются рекомендательными, но повышают выход годных за счет требований к увеличению расстояний между соседними элементами или слоями, расширению проводников и зазоров между ними и т. д. При финальной передаче данных на производство должны проводиться, как минимум: физическая верификация, верификация проекта на соответствие топологии электрической схеме (LVS – Layout Versus Schematic) и проверка соответствия топологии (LVL–Layout Versus Layout). Встроенная система DRC, основанная на геометрических данных конструкции, может предотвратить многочисленные ошибки при выгрузке информации (рис. 1).

Рис. 1. Встроенная система DRC

Рис. 1. Встроенная система DRC

Комплексный процесс верификации может указать на многие критичные места в проекте, которые требуют коррекции. Если эти проблемы не будут обнаружены вовремя, то они могут легко привести к задержке сдачи проекта в производство, дополнительным затратам и сорванным производственным план-графикам выполнения работ. Одним из способов, который может предотвратить данную ситуацию, является реализация подхода проектирования со «сдвигом влево», необходимого для раннего обнаружения и устранения очевидных ошибок при передаче данных по проекту на производство. Использование такого подхода может помочь устранить вовремя более 80% ошибок, избежать задержки при производстве.

Физическая верификация

Одной из отличительных черт верификации ИС является использование нескольких специализированных модулей САПР в рамках единой платформы, позволяющей разработчикам выполнять широкий спектр процессов верификации. Аналогичная цель ставится и при автоматизации проверки конструкций гетерогенных корпусов.

Комплексная верификация значительно упрощается, если исходить из предположения, что каждый отдельный кристалл уже был проверен на соответствие правилам производства на полупроводниковой фабрике. Также крайне важно поддерживать независимость между средой проектирования и средой верификации для обеспечения достоверности результатов проверки.

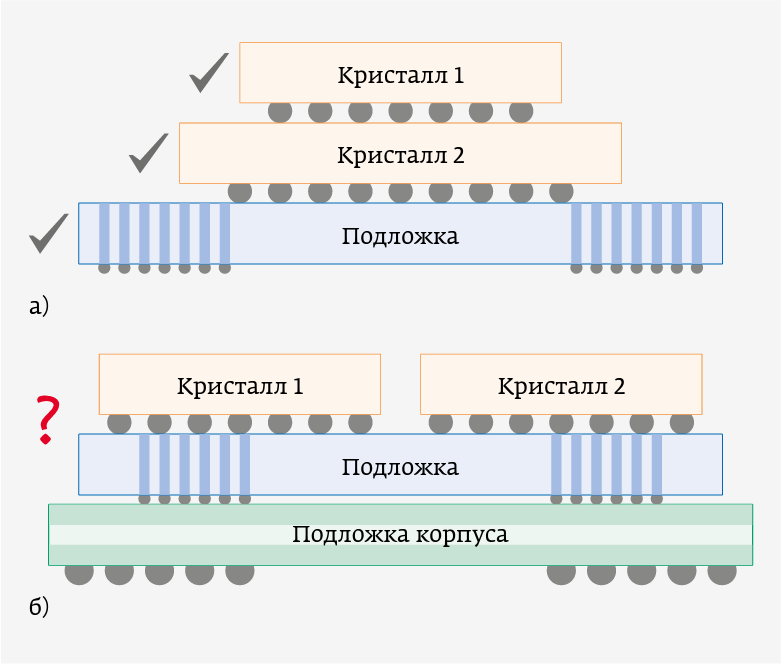

Рис. 2. Верификация отдельных кристаллов и подложек (а), полная LVL / LVS-проверка всей сборки (б)

Рис. 2. Верификация отдельных кристаллов и подложек (а), полная LVL / LVS-проверка всей сборки (б)

Верификация отдельных кристаллов и подложек не является достаточной (рис. 2а), полная LVL / LVS-проверка всей сборки – единственный способ найти обрывы, короткие замыкания или критичные соединения, вызванные неправильно выровненными элементами (рис. 2б).

Верификация включает правила DRC для проверки взаимодействия между элементами кристалла (расстояние между элементами, размеры элементов и т. д.) и может потребовать извлечения нескольких слоев внутри каждого кристалла, чтобы увидеть эти взаимодействия. Физическая верификация также включает в себя проверку совмещения подложек, масштабирования или коэффициентов компенсации, а также совмещение или совпадение площадок.

Программный модуль САПР должен понимать, как различать между собой слои в кристаллах и слои (уровни) размещения элементов на подложке. Используя данные виртуальной модели (цифрового двой ника), Mentor Calibre 3DSTACK автоматически извлекает правильное представление сборки для выполнения DRC- и LVL-проверок и позволяет убедиться, что проект соответствует всем физическим требованиям. Для устранения проблем, связанных с отображением слоев, функционал Calibre 3DSTACK автоматически переназначает все слои для каждого элемента (кристалла, интерпозера, слоев корпуса и т. д.) с целью разделения слоев. Это переназначение должно выполняться после каждой компоновки, для того чтобы избежать проблем, вызванных с многократным размещением одного и того же кристалла.

Компания Mentor Graphics успешно разработала и доказала эффективность PADK, используя технологические модули Calibre 3DSTACK. Комплекс Calibre 3DSTACK был разработан и сертифицирован фирмой STATS ChipPAC, одним из лидеров среди OSAT-компаний, для собственной технологии корпусирования на уровне пластины eWLP. Этот файл правил был адаптирован и проверен при изготовлении микросборки Qualcomm, состоящей из двух кристаллов, соединенных в корпусе с помощью RDL (Redistribution layer, слои перераспределения соединений). Правила STATS ChipPAC включают в себя DRC-правила для слоев корпуса, а также проверяют взаимодействия кристаллов и качество их соединения с корпусом.

Верификация проекта в части соответствия топологии электрической схеме

Проверка LVS для ИС анализирует содержание схемы и соединений, расположение выводов, полученные из топологического представления, и создает физический список цепей (нетлист), который сравнивается с эталонным нетлистом, полученным из электрической схемы. Проверка коммутации выполняется на уровне каждой подложки и между подложками. Автоматизированная LVS-проверка корпуса в простейшем виде должна гарантировать, что в GDSII-файлах интерпозера и корпуса кристаллы правильно соединены между собой (для систем с несколькими кристаллами) и с бампами C4 / BGA (как для однокристальных, так и для многокристальных систем), так как это было заложено в проекте разработчиком.

В гетерогенных корпусах, микросборках эти соединения могут быть между кристаллом и интерпозером; между кристаллом, интерпозером и корпусом; между кристаллом, интерпозером, корпусом и печатной платой. Независимо от исполнения, все начинается с возможности генерации и управления системным нетлистом. Системный нетлист компилируется из виртуальной модели (цифрового двой ника) общей сборки, как обсуждалось ранее. Затем этот системный или «эталонный» нетлист сравнивается с физической схемой проекта, полученной из производственных данных, например GDS в Calibre 3DSTACK. Предупреждения или нарушения могут быть выделены в виртуальной модели, где функциональность Xpedition Substrate Integrator может быть использована для отслеживания и отладки ошибок.

Верификация на уровне гетерогенной микросборки, корпуса

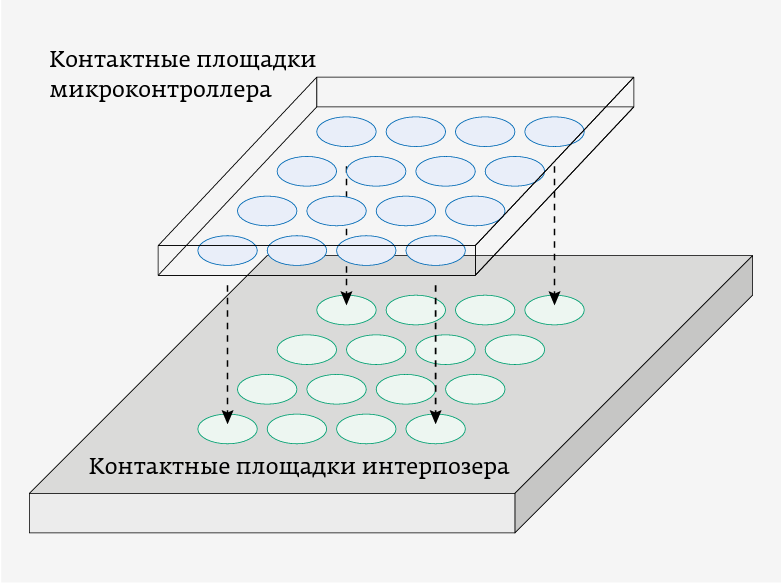

2.5D- и 3D-гетерогенные корпуса, микросборки обычно включают в себя несколько полупроводниковых изделий и несколько подложек для обеспечения необходимых функциональных возможностей и производительности системы. С уменьшением расстояний между кристаллом и подложкой, непосредственная близость этих элементов друг к другу значительно усиливает взаимодействие между микросхемами, что требует унифицированного маршрута совместного проектирования. При использовании критических элементов, таких как высокоскоростные интерфейсы или энергопотребляющие элементы, реализация проекта на одной подложке может приводить к существенному влиянию на соседние подложки или воздействовать на всю систему в целом. Разработчики должны найти способы работать с несколькими подложками в одной среде, при этом взаимодействуя с разными подразделениями, находящимися в разных городах, странах, используя быстрое прототипирование и совместное проектирование для анализа трассировки подложек, электрических и тепловых характеристик, а также тестирования. Поиск оптимального решения может привести к бесконечному числу итераций проекта (рис. 3).

Рис. 3. Совмещение, масштабирование и преобразование пересечений элементов конструкции

Рис. 3. Совмещение, масштабирование и преобразование пересечений элементов конструкции

Физическая верификация гетерогенных корпусов, микросборок широко обсуждалась на различных форумах и конференциях вместе с представлением специальных автоматизированных программных средств [1, 2]. Разработчиками были рассмотрены результаты по применению передовых методов для процесса LVS на уровне сборки, включая необходимые исходные данные (форматы и т. д.) и возможные проблемы. Обсуждался даже вопрос, каким образом можно было бы обеспечить экстракцию паразитных параметров для этих сборок [3–6].

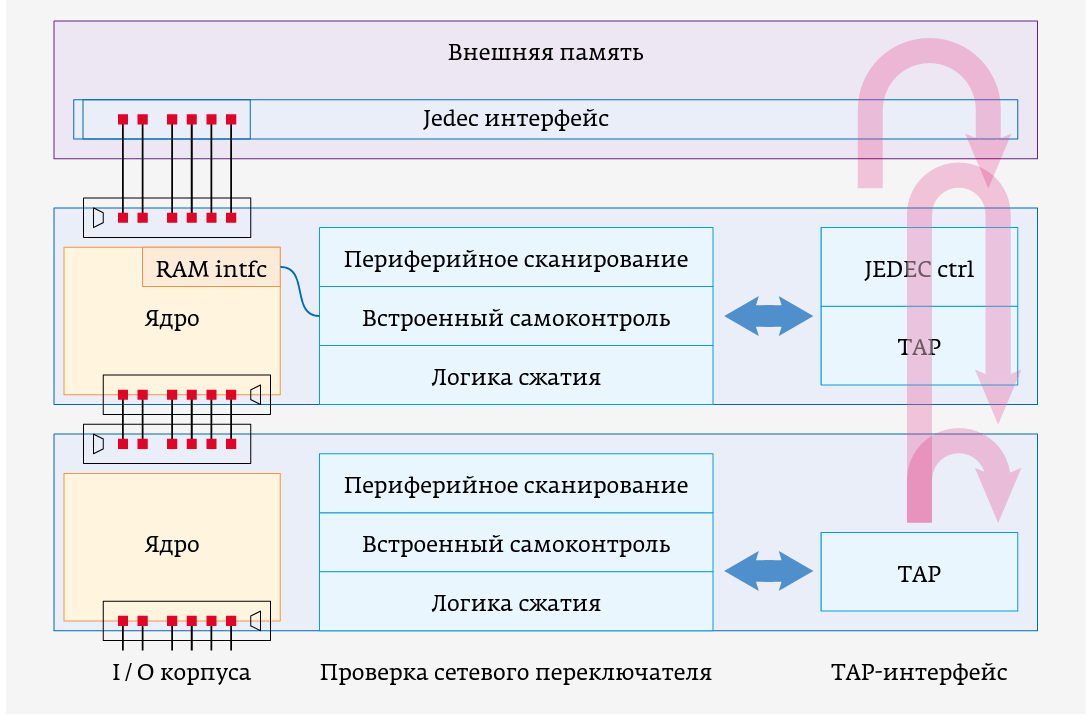

По мере совершенствования технологий и маршрутов проектирования [7-11], разработчики системного уровня также должны знать, достаточно ли DRC-проверки корпуса, проверок LVL (совмещение «кристалл- корпус», масштабирование, ориентация и т. д.) и LVS на уровне сборки, чтобы гарантировать правильную функциональность и успешное изготовление гетерогенной сборки. Для производительного и эффективного тестирования применяется JTAG TAP, верификация сканированием и IJTAG для проверки межсоединений между кристаллами (рис. 4).

Рис. 4. Верификация сканированием и IJTAG для проверки межсоединений между кристаллами

Рис. 4. Верификация сканированием и IJTAG для проверки межсоединений между кристаллами

До недавнего времени не была решена задача создания единой среды, позволяющей разработчикам управлять всеми этими процессами в эффективном, воспроизводимом и автоматизированном маршруте. При комплексном проектировании и верификации разработчики должны уметь контролировать и управлять несколькими подложками (базами данных проектирования) в одной среде. Имея возможность видеть полную картину (кристалл, интерпозер, корпус, печатную плату) в одной среде, разработчики могут лучше предвидеть и устранить потенциальные проблемы, эффективно выполнять и оценивать компромиссные решения и сценарии проектирования, а также в доступной форме сообщать информацию заинтересованным сторонам.

Тестирование

Гарантированно годный кристалл (KGD – knowngooddie) является ключом к эффективному тестированию перед компоновкой кристаллов в 2D и 3D гетерогенные сборки. Генерация тестов на уровне корпуса является очень важным этапом. Группа специалистов по тестированию должна повторно использовать шаблоны встроенного самотестирования (BIST) и сканирования на уровне кристалла, перенося их на уровень корпуса. Тестирование структур межкомпонентных соединений на границе корпуса обеспечивает фактическое соединение ввода-вывода и может выявить любые проблемы, связанные с изготовлением или сборкой подложки. Тестирование неполного стека обычно проводится только на новых процессах или на тех, которые отличаются низким уровнем выхода годных или на которых он ожидается.

Однако, даже при высококачественном тестировании пластин и использовании KGD сборка все равно может привести к сбоям из-за повреждений электростатическим разрядом или из-за контактов, пропущенных при тестировании пластин. При корпусировании многокристальных сборок качество и уровень тестирования пластин имеют решающее значение для поддержания заданного выхода годных.

Программные средства для тестирования логики Tessent™ от компании Mentor предоставляют различные возможности проверки «передовых решений» для тестирования гетерогенных корпусов, в том числе:

- повторное использование шаблонов встроенного самотестирования и сканирования на уровне кристалла;

- использование общего интерфейса порта доступа к средствам тестирования (TAP) для всех уровней подложки;

- использование IJTAG для обеспечения гибкости за счет управления режимами тестовых структур;

- повторное использование шаблонов промежуточного тестирования кристалла на других уровнях подложки корпуса.

Используемые сегодня скорости передачи данных в сочетании с необходимостью потреблять меньше энергии и вырабатывать меньше тепла требуют, чтобы память располагалась в том же корпусе, что и SoC / ASIC. Интеграция нескольких полупроводниковых изделий в одном корпусе позволяет выполнять требования по миниатюризации системы, снижает занимаемое место на плате, производственные затраты и часто повышает качество и надежность.

Данные решения нового поколения для корпусов требуют проверенных, автоматизированных средств получения физических, электрических, тепловых и производственных характеристик в единой среде, которая позволяет разработчикам управлять всеми этими процессами в эффективном, воспроизводимом маршруте проектирования. Время процесса проектирования становится короче, а результаты можно спрогнозировать с высокой точностью до момента запуска проекта в производство.

К. Фелтон1, Д. Вертянов, к. т. н.2, С. Евстафьев, к. т. н.3, В. Сидоренко4, Н. Горшкова, к. т. н.5

Статья впервые опубликована в журнале "ЭЛЕКТРОНИКА: НТБ" № 2 за 2022 год.

__________________________________________________________________________________________________________________

Литература

- Ramadan T. Crossing the chasm: Bringing SoC and package verification together with Calibre 3DSTACK // Mentor, a Siemens business. January 2017. https://go.mentor.com/4QLSO.

- Petranovic D., Chow K. 3D-IC system verification methodology: solutions and challenges // Electronic Design Process Symposium. April 2011. https://www.researchgate.net/publication/268208901 3D-IC System Verification Methodology Solutions and Challenges.

- Ramadan T. Package designers need assembly- level LVS for HDAP verification // Mentor, a Siemens business. December 2017. https://go.mentor.com/4WDVj.

- Decoin C., Kourkoulos V. Fast and accurate extraction of 3D-IC layout structures Mentor, a Siemens business. July 2012.

- Mastroianni T. eSilicon tackles the challenges of advanced IC package design using Xpedition Substrate Integrator and Calibre 3DSTACK. May 2019. https://go.mentor.com/58xrP.

- Amkor Delivers Industry’s First Package Assembly Design Kit to Support Mentor’s High- Density Advanced Packaging Tools. July 2018. https://ir.amkor.com/news-releases/news-release- details/amkor-delivers-industrys-first-package-assemblydesign-kit. www.mentor.com.

- Райнболд К., Фелтон К., Вертянов Д., Никеев К. Проектирование многокристальных модулей и систем в корпусе // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2020. № 2 (00193). С. 144–150.

- Vertyanov D. V., Timoshenkov S. P., Sidorenko V. N., Pogudkin A. V., Belyakov I. A. Effects of Multilayer Structures Made of Epoxy Compounds with Different Filler Contents on Thermo- Mechanical Stresses in 3D packages // Proceedings of the 2021 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering, EIConRus 2021.

- Чугунов Е. Ю., Тимошенков С. П., Погалов А. И., Вертянов Д. В. Конструирование и расчеты трехмерных микроэлектронных модулей с высокой степенью интеграции компонентов // Электронная техника. Серия 3. Микроэлектроника. 2 (178). 2020. С. 42–48.

- Вертянов Д. В., Бураков М. М., Кручинин С. М., Сидоренко В. Н., Брыкин А. В. Трехмерная микросборка на основе коммутационных плат из кремния и бескорпусных элементов МЭМС // НАНОИНДУСТРИЯ. 2018. № S (82). С. 521–531.

- Фергусон Дж., Вертянов Д., Фелтон К., Беляков И., Евстафьев С., Сидоренко В., Горшкова Н. Проектирование корпусов и микросборок по технологии FO WLP средствами сапр Mentor Graphics часть 2 // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2021. № 10 (00211). С. 126–135.

Понравилась статья? Поставьте лайк

Industry Hunter

только что

Industry Hunter

только что