Здесь мы собираем самые интересные статьи, интервью, репортажи и многое другое.

Разработка функциональной схемы 8‑разрядного АЦП последовательного приближения в САПР OrCAD c использованием макромоделей

Строгонов А., Худяков Ю., Белых М.

Моделирование электрических схем с применением современных САПР позволяет исследовать работу схемы без необходимости изготовления прототипа. Для изучения принципов работы 8‑разрядного АЦП последовательного приближения в учебном пособии [1] предлагается собрать и опробовать схему с использованием ИС средней степени интеграции на основе ТТЛ‑ или КМОП‑логики, ЦАП DAC08 и компаратора 311. В статье рассмотрен пример реализации и доработки описанной в [1] функциональной схемы АЦП последовательного приближения в САПР OrCAD с использованием макромоделей ИС серий 74 (ТТЛ) и 74HC (КМОП).

Алгоритм последовательной аппроксимации (приближения) состоит в тестировании каждого бита 8‑разрядного регистра последовательного приближения как в значениях логического 0, так и логической 1, начиная со старшего значащего разряда (СЗР) и заканчивая младшим значащим разрядом (МЗР). Изначально каждый бит D‑триггера 8‑разрядного регистра принимает значение логического 0, а затем в СЗР бит устанавливается равным 1. Если напряжение на выходе ЦАП превышает аналоговое входное напряжение, бит возвращается в 0, в противном случае он остается равным 1.

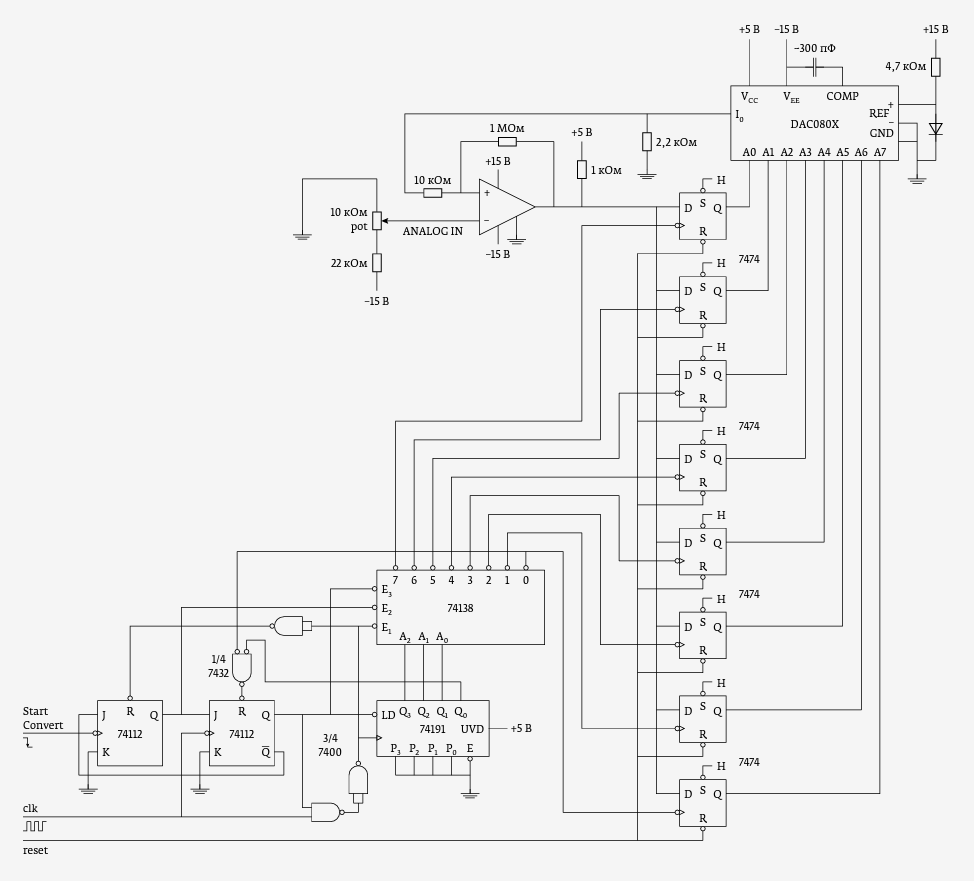

Рис. 1. Функциональ ная схема АЦП из работы [2]

Рис. 1. Функциональ ная схема АЦП из работы [2]

Логическая часть схемы АЦП реализована на JK‑триггерах 74112, 4‑разрядном реверсивном двоичном счетчике 74191 с возможностью загрузки параллельным кодом и дешифраторе 3 × 8 74138 и вспомогательная схема управления на логических элементах (рис. 1). Схема приводится в том виде, как она представлена в работе [2] – оригинальном издании учебного пособия [1]. Дешифратор 74138 (обеспечивает код на выходе «1 из 8») направляет тактовые импульсы на каждый триггер по очереди. Компаратор на ОУ 311 сравнивает выходной сигнал ЦАП с аналоговым входом, а его выход подключен к D‑входу каждого триггера. DAC080x – это ЦАП с потребляемым током, поэтому его выходной сигнал становится более отрицательным, когда цифровой вход увеличивается от 0 до 255 (в инструкции на применение DAC0808 National Semiconductor приводится типовая схема включения ЦАП с токовым выходом с ОУ LF351 в инвертирующем включении). Связка «ЦАП – ОУ» обеспечивает отрицательную обратную связь: если выход ЦАП слишком отрицательный, текущий адресуемый бит устанавливается в 0, чтобы повысить выходное напряжение ЦАП; если выход ЦАП слишком положительный, бит устанавливается в 1, чтобы его понизить.

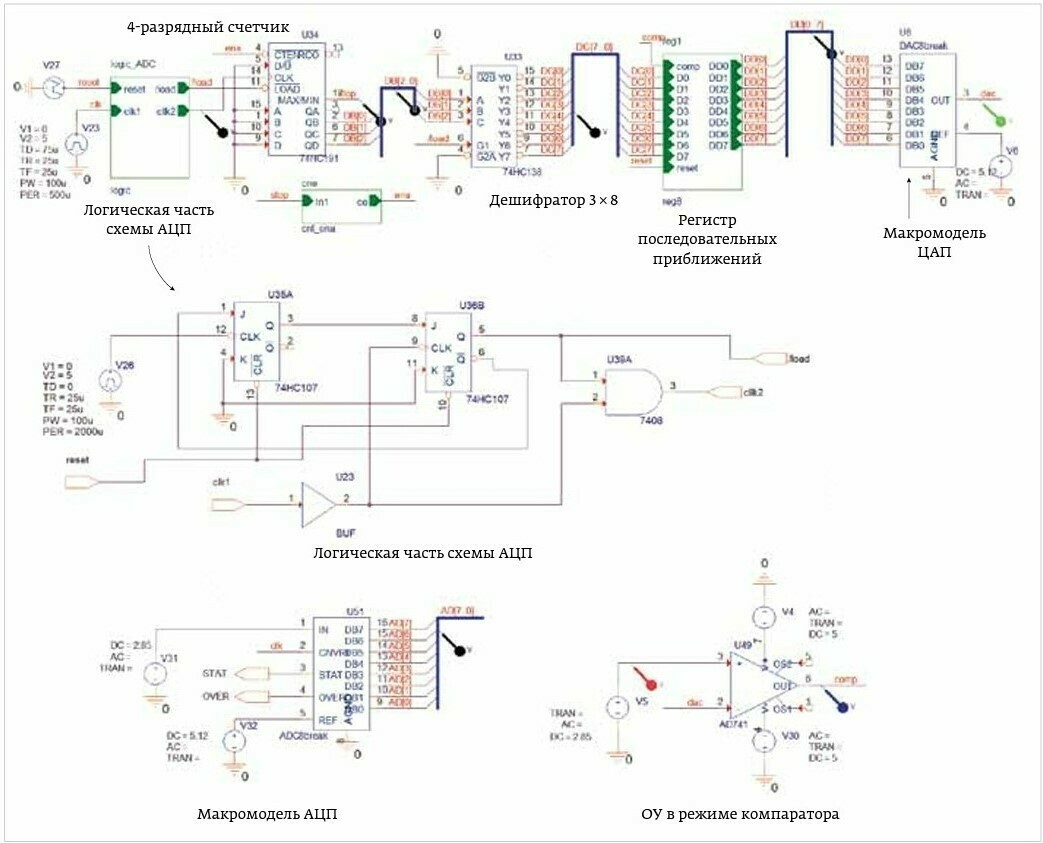

Рис. 2. Проект АЦП последовательного приближения в САПР OrCAD

Рис. 2. Проект АЦП последовательного приближения в САПР OrCAD

Разработаем проект АЦП в САПР OrCAD. Для этого JK‑триггер 74 серии 74112 заменим на аналогичный JK‑триггер 74HC107 серии 74HC. Счетчик 74191 заменим на 74HC191, а дешифратор 3 × 8 74138 – на 74HC138. В логической части схемы откажемся от управления асинхронными сбросами JK‑триггеров с помощью логических элементов (рис. 2). Для завершения процесса преобразования будем использовать выходной сигнал MAX / MIN счетчика 74HC191. Таким образом, полный цикл преобразования будет совершаться за 16 тактов синхрочаcтоты.

Для того чтобы по выходам дешифратора 74HC138 «побежал» логический 0 (активный низкий уровень сигнала), необходимо входы сконфигурировать следующим образом: вход G1 подключить к выходу JK‑триггера U36B, который связан с сигналом загрузки LOAD (активный низкий) счетчика 74HC191, а два других входа, G2A и G2B, заземлить.

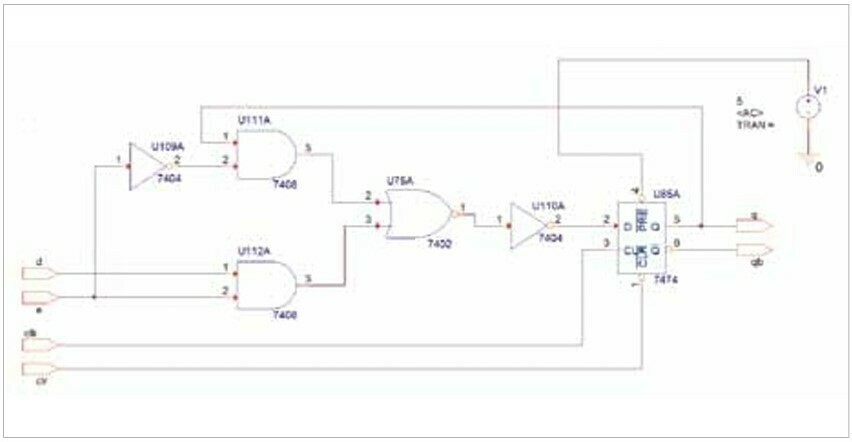

Рис. 3. D‑триггер, тактируемый фронтом синхроимпульса, с асинхронным входом разрешения записи

Рис. 3. D‑триггер, тактируемый фронтом синхроимпульса, с асинхронным входом разрешения записи

Для реализации механизма последовательных приближений необходимо в схему из [1] внести некоторые изменения. А именно, доработаем D‑триггер 7474, тактируемый передним фронтом синхроимпульса, таким образом, чтобы он превратился в D‑триггер с асинхронным входом разрешения e (enable) записи информационного сигнала (рис. 3). Для этого на вход D подключим мультиплексор 2 × 1. Вход e подключим к «питанию» (не будем использовать), а записанную в триггер информацию снимем с инверсного выхода Q. Наличие входа разрешения записи информации в триггер обеспечивает возможность дальнейшей модернизации схемы АЦП, поскольку тактирование выходами дешифратора не является хорошим решением, а используется скорее для демонстрации принципов работы схемы. Например, вместо связки счетчик‑ дешифратор можно было бы использовать сдвиговый регистр. В этом случае все триггеры в проекте тактировались бы одним синхросигналом.

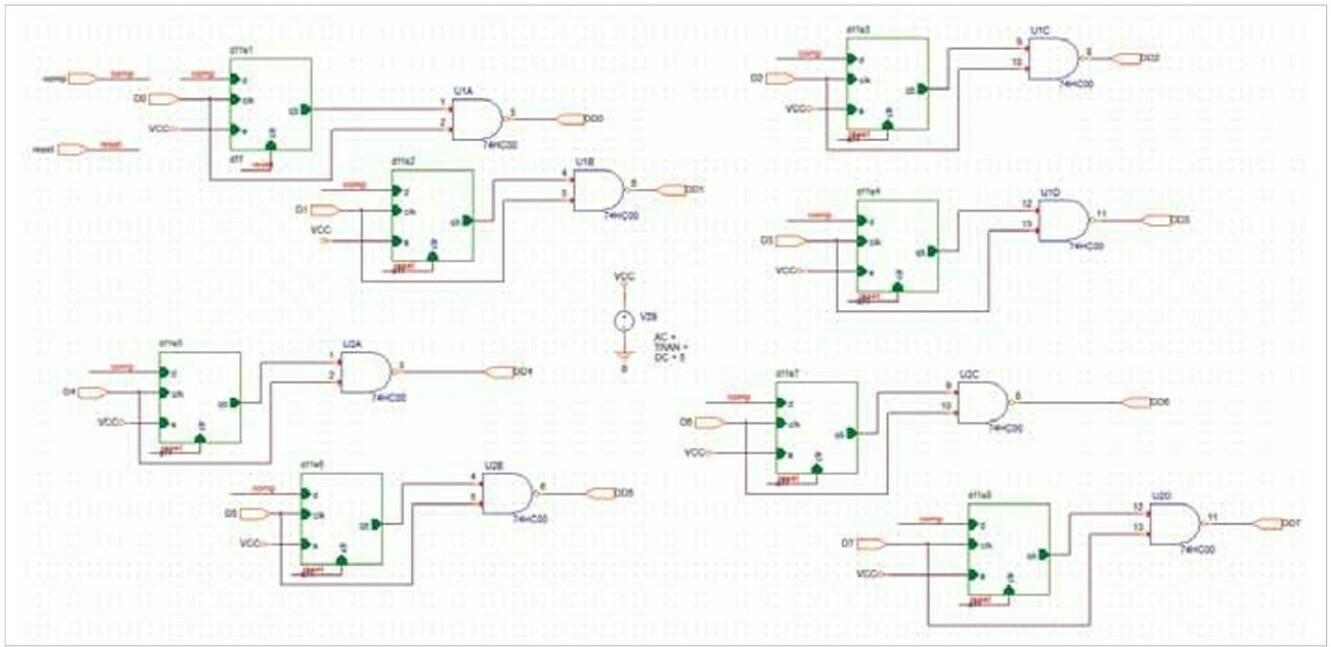

Далее создадим иерархический блок dff и организуем 8‑разрядный параллельный регистр. На информационные входы триггеров dff будем подавать выходной сигнал с компаратора, а на синхросигналы триггеров подключим выводы дешифратора 3 × 8 (рис. 4).

Рис. 4. Регистр последовательных приближений

Рис. 4. Регистр последовательных приближений

Для правильного формирования результата регистром необходимо на инверсные выходы восьми триггеров dff подключить один из входов логических элементов 2И‑НЕ, а на вторые входы – выходы дешифратора. Далее объединим восемь триггеров и «обрамляющую» логику на элементах 2И‑НЕ в иерархический блок reg8 и назовем его «регистром последовательных приближений» (РПП), точнее, его надо было бы назвать регистр формирования результата (см. рис. 4). Такое решение позаимствуем из работы [3].

Выходы РПП подключаются к ЦАП на основе макромодели DAC8break с опорным напряжением Vref = 5,12 В в следующем порядке: DD[0] – старший значащий разряд (СЗР), DD[7] – младший значащий разряд (МЗР). Аналоговый выходной сигнал ЦАП dac подключен к компаратору на основе макромодели ОУ AD741 (два источника опорного напряжения 5 и –5 В), на другой вход которого подключен сигнал, подлежащий преобразованию в цифровой код (см. рис. 2).

Для проверки правильности работы разработанного АЦП используем макромодель параллельного АЦП ADC8break с опорным напряжением 5,12 В, которая выдает оцифрованный аналоговый сигнал за один такт синхроимпульса.

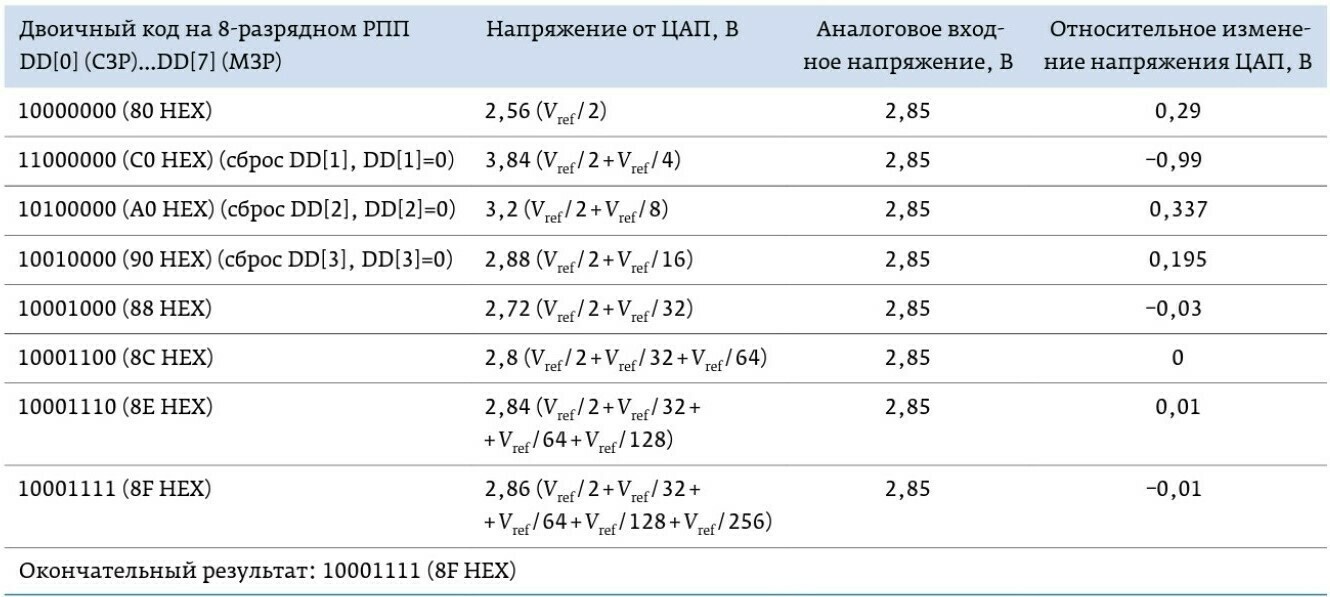

Таблица 1. Работа АЦП последовательного приближения при преобразовании аналогового напряжения 2,85 В в цифровой код при опорном напряжении 5,12 В

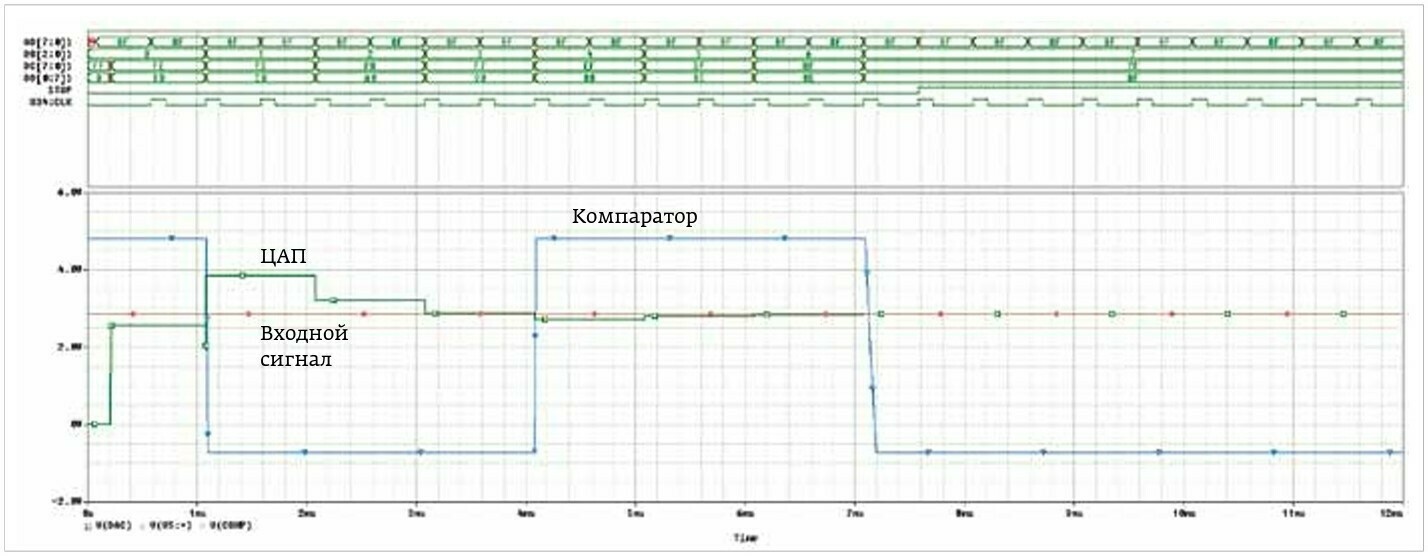

Продемонстрируем принцип работы АЦП на примере преобразования аналогового напряжения 2,85 В в цифровой код (табл. 1, рис. 5). В верхней части рис. 5 (в верхнем окне для вывода цифровых сигналов) показан двоичный код на 8‑разрядном РПП (шина DD[7..0] и побитно DD0, ... DD7) в процессе преобразования аналогового сигнала в цифровой код. А в нижней части рис. 5 (в нижнем окне для вывода аналоговых сигналов) показаны выходной сигнал ЦАП, компаратора и оцифровываемый входной сигнал. Моделирование показало, что цифровые коды на выходах двух АЦП при преобразовании аналогового напряжения 2,85 В в цифровой код совпадают и составляют 8F.

Рис. 5. Временные диаграммы преобразования аналогового напряжения 2,85 В в цифровой код 8F HEX

Рис. 5. Временные диаграммы преобразования аналогового напряжения 2,85 В в цифровой код 8F HEX

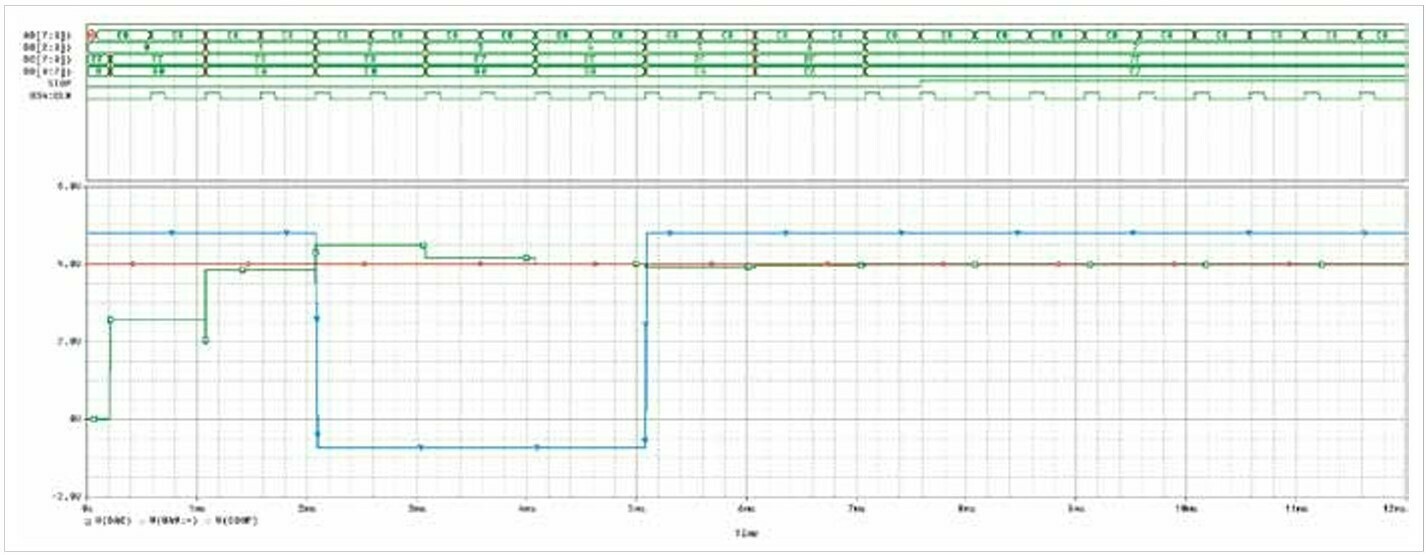

Рис. 6. Временные диаграммы преобразования аналогового напряжения 4 В в цифровой код

Рис. 6. Временные диаграммы преобразования аналогового напряжения 4 В в цифровой код

На рис. 6 показаны временные диаграммы преобразования аналогового напряжения 4 В в цифровой код. Макромодель АЦП ADC8break выдает код С8 (200 DEC), а доработанная схема АЦП – код С7 (199 DEC). Это говорит о том, что доработанная схема, в отличие от идеальной макромодели ADC8break, имеет незначительную погрешность преобразования.

ЗАКЛЮЧЕНИЕ

В случае реализации предложенной в [1] схемы в САПР OrCAD необходимо предусмотреть логику формирования результата работы регистра последовательного приближения. Доработанный вариант АЦП способен преобразовать входное напряжение в цифровой код за 16 тактов синхрочастоты (восемь внутренних циклов при тактировании РПП выходами дешифратора 74HC138). Работа АЦП протестирована в диапазоне входных напряжений от 0,1 до 4,9 В.

Доработанный вариант схемы АЦП последовательного приближения может быть использован для изучения основ аналого‑ цифрового преобразования в САПР OrCAD без использования макетной платы.

А. Строгонов, д. т. н.1, Ю. Худяков, к. т. н.2, М. Белых 3

Статья впервые опубликована в журнале "ЭЛЕКТРОНИКА: НТБ" № 3 за 2022 год.

____________________________________________________________________________________________________

ЛИТЕРАТУРА

-

Каплан Д., Уайт К. Практические основы аналоговых и цифровых схем. М.: ТЕХНОСФЕРА, 2006. 176 с.

-

Kaplan D. M., White C. G. Hands‑ On Electronics. APractical Introduction to Analog and Digital Circuits. Cambridge university press, 2003// www.cambridge.org/9780521815369.

-

Строгонов А. Изучение принципов работы ЦАП и АЦП с помощью средств смешанного аналого‑ цифрового моделирования САПР OrCAD// Компоненты и технологии, 2007. № 11. C.137–143.

Понравилась статья? Поставьте лайк

Industry Hunter

только что

Industry Hunter

только что